時鐘芯片的低功耗設計案例

2020-09-30 15:15:59閱讀量:925

時鐘芯片廣泛地應用于各種需要記錄特定時間的設備中。對于便攜式設備,時鐘芯片的功耗對維持整個系統的正常時間記錄是非常重要的。芯片具有較低的功耗,可以滿足更長的工作時間要求。在嵌入式系統中,時鐘芯片是工作頻率較高的電路,降低其功耗,對于整個系統的功耗降低有著顯著的作用。

本文采用自頂而目的設計原則,從體系結構到電路實現上分層次探討了時鐘芯片的功耗來源,并采取相應的控制手段實現芯片的低功耗設計。

1.1 CMOS電路功耗分析

對于CMOS集成電路,影響功耗的因素主要包括三個部門:動態功耗、短路功耗和靜態功耗。由于動態功耗占CMOS電路總功耗的80%以上,因此在功耗設計上主要考慮如何降低這部分功耗。

動態功耗Pd可用下式表示:

式中,CL為輸出節點的總負載電容;VDD為工作電壓,也是CMOS電路的邏輯擺幅;f0→1為開關活性因子。下面就來分析與時鐘芯片功耗設計密切相關的兩個因素。

1.1.1 功耗與工作電壓VDD的關系

從(1)式中可以看出,降低工作電壓會使功耗呈平方律下降,因此絕大多數低功耗設計都首先考慮采用盡可能低的工作電壓。但對于確定的工藝,如果電源電壓過低,將會導致電路性能下降。當電源電壓降低到接近PMOS和NMOS晶體管的閾值電壓值之和時,延遲時間急劇增大,器件的工作速度下降,功耗反而增加。

1.1.2 功耗與開關活性因子f0→1的關系

對于CMOS邏輯器件,只有當輸出節點出現0到1的邏輯轉換時,才從電源吸引能量。因此影響開關活性因子的因素有兩個,一個是輸入信號變化頻率,另一個是電路的邏輯類型、所實現的功能和整個網絡的拓撲結構。對于開關活性因子?0→1,可用下式表示:

式中,P0→1是器件開關的概率,即輸入從0到1發生轉變的概率,它和組成電路的邏輯類型有關。f為輸入信號變化的頻率,即器件工作頻率。由(2)式可知,器件的開關概率P0→1和工作頻率f與動態功耗成正比。

此外,COMS門的充電時間和節點負載電容等都是影響功耗的因素,需要在電路的具體實現中加以控制。

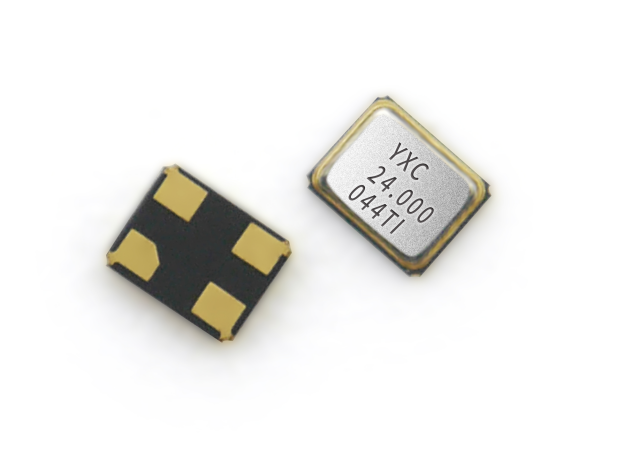

1.2 時鐘電路低功耗分析

1.2μmCMOS電路的標準工作電壓為5V,這對于工作頻率較高的電路而言,功耗是非常大的。為降低芯片的整體功耗,考慮在開關活性因子較高的電路上采用低于給定工作電壓的設計。由時鐘芯片的工作原理可知,時鐘信號發生器是整個芯片中工作頻率最高的電路,它包括振蕩電路和分頻電路兩部分。其中,振蕩電路的工作頻率與外接晶振的頻率相同,器件開關因子最高,功耗最大。如果能夠降低這部門MOS器件的工作電壓,合理地設計主要功耗元件的特性參數,降低工作電流,就可以有效地降低功耗;分頻電路,尤其是工作在前面幾級的分頻電路,器件的開關活性因子也很高。因此在分頻電路中,同樣采用降低工作電壓的方法來降低功耗。通過電路功能分析可知,前面1:8分頻的電路的工作頻率是最高的,這部分電路的功耗占整個分頻電路總功耗的80%左右,因此低功耗設計應以降低這部分電路的功耗為目標。

2 低功耗時鐘信號發生器電路設計

低功耗時鐘信號發生器總體設計電路圖如圖1所示。

本文采用自頂而目的設計原則,從體系結構到電路實現上分層次探討了時鐘芯片的功耗來源,并采取相應的控制手段實現芯片的低功耗設計。

1.1 CMOS電路功耗分析

對于CMOS集成電路,影響功耗的因素主要包括三個部門:動態功耗、短路功耗和靜態功耗。由于動態功耗占CMOS電路總功耗的80%以上,因此在功耗設計上主要考慮如何降低這部分功耗。

動態功耗Pd可用下式表示:

Pd=C L V DD2f0→1 (1)

式中,CL為輸出節點的總負載電容;VDD為工作電壓,也是CMOS電路的邏輯擺幅;f0→1為開關活性因子。下面就來分析與時鐘芯片功耗設計密切相關的兩個因素。

1.1.1 功耗與工作電壓VDD的關系

從(1)式中可以看出,降低工作電壓會使功耗呈平方律下降,因此絕大多數低功耗設計都首先考慮采用盡可能低的工作電壓。但對于確定的工藝,如果電源電壓過低,將會導致電路性能下降。當電源電壓降低到接近PMOS和NMOS晶體管的閾值電壓值之和時,延遲時間急劇增大,器件的工作速度下降,功耗反而增加。

1.1.2 功耗與開關活性因子f0→1的關系

對于CMOS邏輯器件,只有當輸出節點出現0到1的邏輯轉換時,才從電源吸引能量。因此影響開關活性因子的因素有兩個,一個是輸入信號變化頻率,另一個是電路的邏輯類型、所實現的功能和整個網絡的拓撲結構。對于開關活性因子?0→1,可用下式表示:

f0→1=P 0→1 f (2)

式中,P0→1是器件開關的概率,即輸入從0到1發生轉變的概率,它和組成電路的邏輯類型有關。f為輸入信號變化的頻率,即器件工作頻率。由(2)式可知,器件的開關概率P0→1和工作頻率f與動態功耗成正比。

此外,COMS門的充電時間和節點負載電容等都是影響功耗的因素,需要在電路的具體實現中加以控制。

1.2 時鐘電路低功耗分析

1.2μmCMOS電路的標準工作電壓為5V,這對于工作頻率較高的電路而言,功耗是非常大的。為降低芯片的整體功耗,考慮在開關活性因子較高的電路上采用低于給定工作電壓的設計。由時鐘芯片的工作原理可知,時鐘信號發生器是整個芯片中工作頻率最高的電路,它包括振蕩電路和分頻電路兩部分。其中,振蕩電路的工作頻率與外接晶振的頻率相同,器件開關因子最高,功耗最大。如果能夠降低這部門MOS器件的工作電壓,合理地設計主要功耗元件的特性參數,降低工作電流,就可以有效地降低功耗;分頻電路,尤其是工作在前面幾級的分頻電路,器件的開關活性因子也很高。因此在分頻電路中,同樣采用降低工作電壓的方法來降低功耗。通過電路功能分析可知,前面1:8分頻的電路的工作頻率是最高的,這部分電路的功耗占整個分頻電路總功耗的80%左右,因此低功耗設計應以降低這部分電路的功耗為目標。

2 低功耗時鐘信號發生器電路設計

低功耗時鐘信號發生器總體設計電路圖如圖1所示。

希望大家對時鐘芯片的低功耗設計過程有所了解。

內容聲明:本文轉載自其它來源,轉載目的在于傳遞更多信息,不代表立創商城贊同其觀點和對其真實性負責,僅作學習與交流目的使用。

熱門物料

型號

價格

| LM1117IMPX-3.3/NOPB/線性穩壓器(LDO) | 0.7147 | |

| DRV8874PWPR/有刷直流電機驅動芯片 | 3.45 | |

| LM358BIDR/運算放大器 | 0.35 | |

| LMR33630ADDAR/DC-DC電源芯片 | 2.01 | |

| LM5164DDAR/DC-DC電源芯片 | 3.19 | |

| ADS1299IPAGR/模擬前端(AFE) | 222.43 | |

| TPS82130SILR/DC-DC電源模塊 | 6.13 | |

| TPL5010DDCR/定時器/計時器 | 1.0884 | |

| LM27762DSSR/電荷泵 | 3.11 | |

| TLV9062IDR/運算放大器 | 0.3242 |