華為首次公開主芯片堆疊封裝專利

2022-05-07 18:08:22閱讀量:590

導(dǎo)讀:據(jù)國家知識產(chǎn)權(quán)局,5月6日,華為公布了一項(xiàng)關(guān)于“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”的專利,涉及主芯片和多個(gè)副芯片的堆疊封裝。

圖:華為專利信息

國家知識產(chǎn)權(quán)局信息顯示,這項(xiàng)專利早在2019年10月30日就申請了,但時(shí)隔兩年半才公開,發(fā)明人是張童龍、張曉東、官勇、王思敏。

該專利描述了一種芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備,涉及電子技術(shù)領(lǐng)域,用于解決如何將多個(gè)副芯片堆疊單元可靠的鍵合在同一主芯片堆疊單元上的問題。

這或許意味著,華為早在2019年就開始為繞開先進(jìn)工藝、通過堆疊設(shè)計(jì)主芯片做技術(shù)儲備。

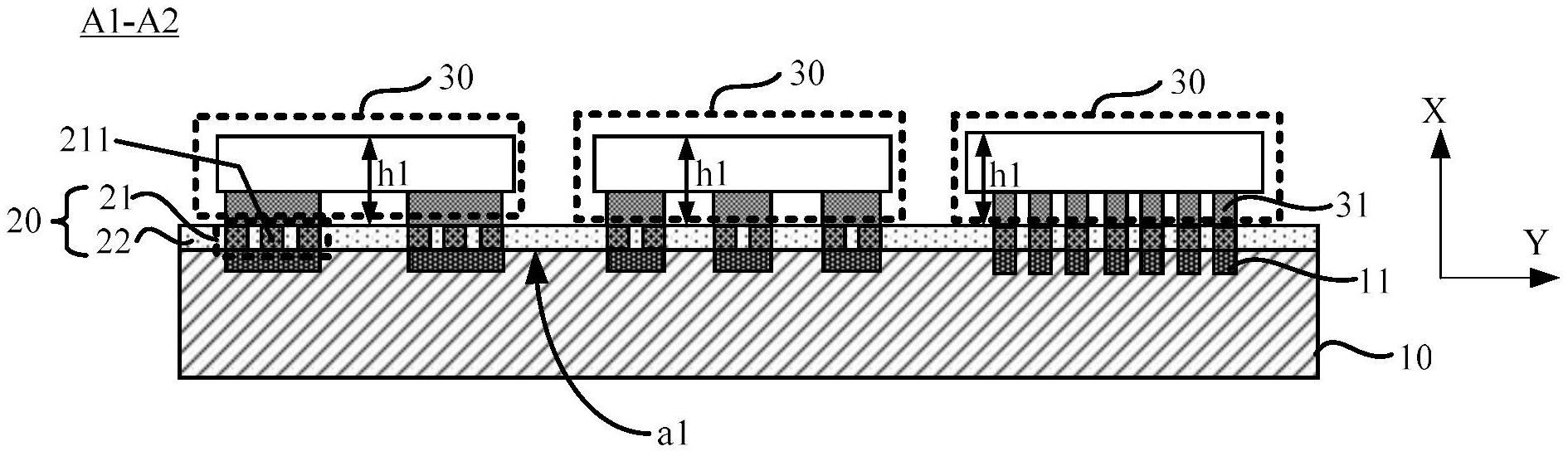

圖:華為芯片堆疊封裝專利

根據(jù)專利信息,華為描述的芯片堆疊封裝結(jié)構(gòu)包括:

1、主芯片堆疊單元(10),具有位于第一表面上的絕緣且間隔設(shè)置的多個(gè)主管腳(11);

2、第一鍵合層(20),設(shè)置于第一表面上;第一鍵合層(20)包括絕緣且間隔設(shè)置的多個(gè)鍵合組件(21);

3、多個(gè)鍵合組件(21)中的每個(gè)包括至少一個(gè)鍵合部(211),任意兩個(gè)鍵合部(211)絕緣設(shè)置,且任意兩個(gè)鍵合部(211)的橫截面積相同;

4、多個(gè)鍵合組件(21)分別與多個(gè)主管腳(11)鍵合;

5、多個(gè)副芯片堆疊單元(30),設(shè)置于第一鍵合層(20)遠(yuǎn)離主芯片堆疊單元(10)一側(cè)的表面;

6、副芯片堆疊單元(30)具有絕緣且間隔設(shè)置的多個(gè)微凸點(diǎn)(31);

7、多個(gè)微凸點(diǎn)(31)中的每個(gè)與多個(gè)鍵合組件(21)中的一個(gè)鍵合。

圖:華為芯片堆疊封裝專利

而4月初,芯片大師曾報(bào)道首次公開!菊廠芯片堆疊技術(shù)來了,華為就已經(jīng)公開了一種芯片堆疊封裝及終端設(shè)備專利,涉及半導(dǎo)體技術(shù)領(lǐng)域,能夠在保證供電需求的同時(shí),解決因采用硅通孔技術(shù)而導(dǎo)致的成本高的問題。

而在3月底的華為2021年年報(bào)發(fā)布會上,華為輪值董事長郭平表示,未來華為可能會采用多核結(jié)構(gòu)的芯片設(shè)計(jì)方案,以提升芯片性能,同時(shí),采用面積換性能、用堆疊換性能的方法,使得不那么先進(jìn)的工藝,也能持續(xù)讓華為在未來的產(chǎn)品里面,能夠具有競爭力。

- 0402這么好焊?!小伙做了個(gè)吸筆,貼片都變輕松了……

- 特爾又雙叒有新動(dòng)作了!重心轉(zhuǎn)向14A工藝、重組玻璃基板

- FPGA其實(shí)不難!做了這個(gè)示波器之后,我好像真學(xué)會了……

- 用STM32,做了一個(gè)“單手”鍵盤!開源了……

- 汽車芯片難做,芯片設(shè)計(jì)大廠考慮出售!

- 重磅!全棧自研國產(chǎn)CPU芯片,龍芯3C6000發(fā)布!

- HCI杭晶電子:TCXO系列晶振在對講機(jī)系列中的應(yīng)用

- XBLW-INA180/INA181電流檢測放大器的優(yōu)質(zhì)選擇

- 香港電阻RCA系列:性能革新,重塑成本優(yōu)勢!

- 500W像素!用香橙派,做了個(gè)視覺模塊!以后調(diào)試,維修,就用它了!