電路設計中抑制或削弱反射波干擾的5種方法

2017-08-07 11:10:54閱讀量:16317來源:立創商城

CMOS系列或HC系列器件的輸入阻抗很高,在使用中除容易引起靜電干擾外,還容易傳輸反射波干擾。因此在長線傳輸使用時需要注意采取相應措施來抑制或削弱反射波,本文從降低阻抗和長線驅動兩個方面,提供了5個解決方法。

1、阻抗匹配

根據反射理論,當傳輸線的特性阻抗與負載電阻相等時,反射將不會發生。即阻抗不匹配是造成信號在傳輸線上反射的原因。實際的電路實現中阻抗不匹配是絕對的,而匹配是相對的。

引起阻抗不匹配的原因有多種,由驅動源、傳輸線和負載的阻抗不同可引起阻抗不匹配、傳輸線的不連續,例如導通孔、短截線也可引起阻抗不匹配;另外由于返回路徑上局部電感、電容的變化、返回路徑不連續也會導致阻抗不連續。其中,由驅動源、傳輸線和負載的阻抗不同引起的阻抗不匹配是最主要的原因。

阻抗匹配方法有以下幾種:

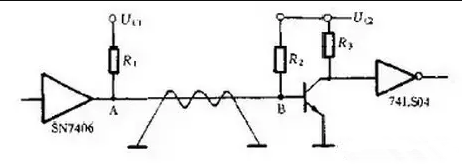

2、采用輸入/輸出驅動器

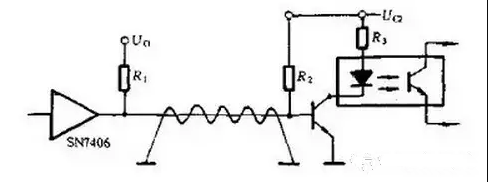

如下圖所示

當A點為低電平時,反射波從B向A傳輸。由于此時驅動器的輸出阻抗幾乎為零,反射信號一到達該輸出端就有相當部分被吸收掉,只剩下部分信號繼續反射。也就時說,由于反射信號遇到的時低阻抗,它的反射能力大大減弱。當A點為高電平時,發送器的輸出阻抗很大,可視為開路,為了降低接收器的輸入阻抗,接入一個負載電阻,這樣就大大削弱了反射波的干擾。

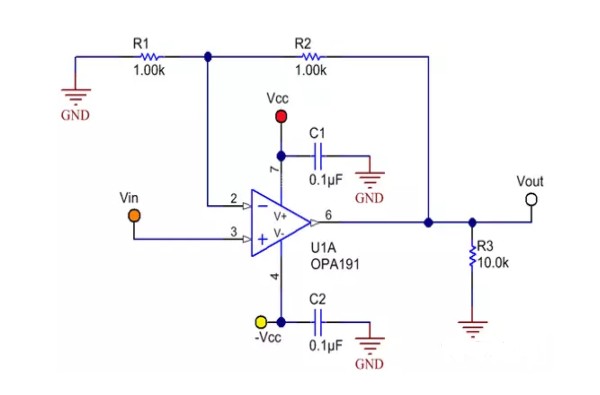

3、降低輸入阻抗

如下圖所示

當驅動器輸出低電平時,A點對地阻抗很低;當驅動器輸出高電平時,B點對地阻抗也很低。由此可見,無論是輸出高電平還是低電平,反射波都將很快衰減。

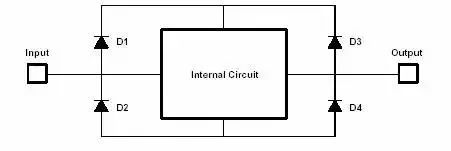

4、采用光電耦合

除可有效抑制反射波干擾外,還實現了信號地隔離。

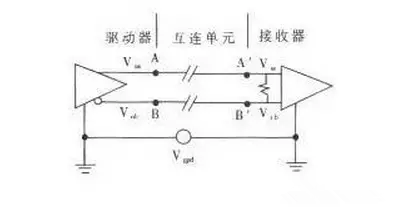

5、采用差分傳輸技術

使用差分信號進行長線傳輸有一個很重要的原因是噪聲以共模的方式在一對差分線上耦合出現,并在接收器中相減從而可消除噪聲。

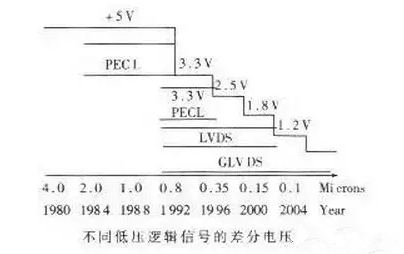

常用的差分傳輸技術有ECL、PECL、LVDS及GLVDS.

ECL和PECL技術的信號擺幅依賴于供電電壓,ECL要求負的供電電壓,PECL使用正的供電電壓。GLVDS是一種發展中的尚未確定的新技術,使用500mV的供電電壓可提供250mV 的信號擺幅。

LVDS物理接口使用1.2V偏置提供400mV擺幅的信號,其驅動器和接收器不依賴于特定的供電電壓。LVDS驅動器由一個驅動差分線對的電流源組成,通常電流為3.5mA,接收器具有很高的輸入阻抗,因此驅動器輸出的電流大部分都流過100Ω的匹配電阻,并在接收器的輸入端產生大約350mA 的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯″1″和邏輯″0″狀態。低擺幅驅動信號實現了高速操作并減小了功率消耗,差分信號提供了適當噪聲邊緣和功率消耗大幅減少的低壓擺幅。終端電阻100Ω,不僅終止了環流信號,同時防止信號在終端發生反射。如下圖所示:

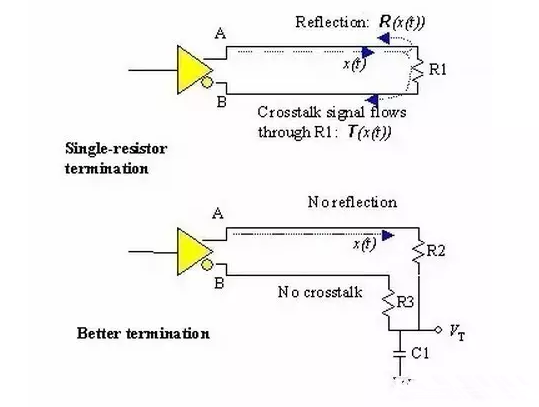

差分傳輸方式的終端匹配方法比較:

如下圖所示的兩種差分傳輸方式的終端方法,第一種方法采用單電阻終端,第二種方法采用雙電阻終端。

第一種方法對差模信號進行匹配,但不對共模信號匹配。在共模干擾比較理想的情況(干擾信號同時到達A、B線,并且幅度相同)下可以很好的工作,但由于布線等原因造成A、B傳輸線受干擾情況不完全一致時,干擾信號會在傳輸線上來回反射,特別是在傳輸時鐘信號,并且傳輸線延時等于1/4時鐘周期時,干擾信號可能在線路上來會反射形成自激。

第二種方法對每條傳輸線單獨進行匹配,該方法對共模信號和差模信號同時匹配,故不會在傳輸線上產生反射。

| LM1117IMPX-3.3/NOPB/線性穩壓器(LDO) | 0.7147 | |

| DRV8874PWPR/有刷直流電機驅動芯片 | 3.45 | |

| LM358BIDR/運算放大器 | 0.35 | |

| LMR33630ADDAR/DC-DC電源芯片 | 2.01 | |

| LM5164DDAR/DC-DC電源芯片 | 3.19 | |

| ADS1299IPAGR/模擬前端(AFE) | 222.43 | |

| TPS82130SILR/DC-DC電源模塊 | 6.13 | |

| TPL5010DDCR/定時器/計時器 | 1.0884 | |

| LM27762DSSR/電荷泵 | 3.11 | |

| TLV9062IDR/運算放大器 | 0.3242 |