一顆芯片成本到底要多少錢?

2018-01-09 13:42:40閱讀量:18394來源:立創(chuàng)商城

集成電路產(chǎn)業(yè)的特色是贏者通吃,像Intel這樣的巨頭,巔峰時期的利潤可以高達60%。

那么,相對應(yīng)動輒幾百、上千元的CPU,它的實際成本到底是多少呢?

芯片的硬件成本構(gòu)成

芯片的成本包括芯片的硬件成本和芯片的設(shè)計成本。

芯片硬件成本包括晶片成本+掩膜成本+測試成本+封裝成本四部分(像ARM陣營的IC設(shè)計公司要支付給ARM設(shè)計研發(fā)費以及每一片芯片的版稅,但筆者這里主要描述自主CPU和Intel這樣的巨頭,將購買IP的成本省去),而且還要除去那些測試封裝廢片。

用公式表達為:

芯片硬件成本=(晶片成本+測試成本+封裝成本+掩膜成本)/ 最終成品率

對上述名稱做一個簡單的解釋,方便普通群眾理解,懂行的可以跳過。

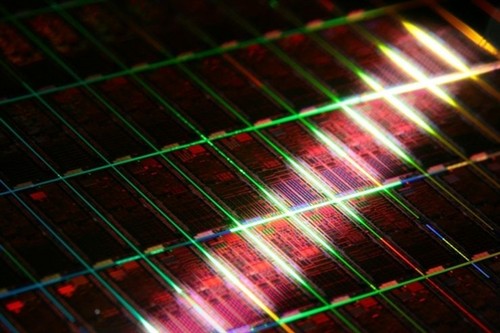

從二氧化硅到市場上出售的芯片,要經(jīng)過制取工業(yè)硅、制取電子硅、再進行切割打磨制取晶圓。晶圓是制造芯片的原材料,晶片成本可以理解為每一片芯片所用的材料(硅片)的成本。一般情況下,特別是產(chǎn)量足夠大,而且擁有自主知識產(chǎn)權(quán),以億為單位量產(chǎn)來計算的話,晶片成本占比最高。不過也有例外,在接下來的封裝成本中介紹奇葩的例子。

封裝是將基片、內(nèi)核、散熱片堆疊在一起,就形成了大家日常見到的CPU,封裝成本就是這個過程所需要的資金。在產(chǎn)量巨大的一般情況下,封裝成本一般占硬件成本的5%-25%左右,不過IBM的有些芯片封裝成本占總成本一半左右,據(jù)說最高的曾達到過70%......

測試可以鑒別出每一顆處理器的關(guān)鍵特性,比如最高頻率、功耗、發(fā)熱量等,并決定處理器的等級,比如將一堆芯片分門別類為:I5 4460、I5 4590、I5 4690、I5 4690K等,之后Intel就可以根據(jù)不同的等級,開出不同的售價。不過,如果芯片產(chǎn)量足夠大的話,測試成本可以忽略不計。

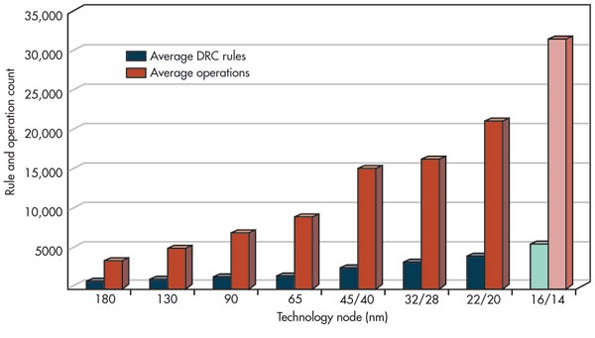

掩膜成本就是采用不同的制程工藝所需要的成本,像40/28nm的工藝已經(jīng)非常成熟,成本也低——40nm低功耗工藝的掩膜成本為200萬美元;28nm SOI工藝為400萬美元;28nm HKMG成本為600萬美元。

(光刻機掩膜臺曝光)

不過,在先進的制程工藝問世之初,耗費則頗為不菲——在2014年剛出現(xiàn)14nm制程時,其掩膜成本為3億美元(隨著時間的推移和臺積電、三星掌握14/16nm制程,現(xiàn)在的價格應(yīng)該不會這么貴);而Intel正在研發(fā)的10nm制程。根據(jù)Intel官方估算,掩膜成本至少需要10億美元。不過如果芯片以億為單位量產(chǎn)的話(貌似蘋果每年手機+平板的出貨量上億),即便掩膜成本高達10億美元,分攤到每一片芯片上,其成本也就10美元。而這從另一方面折射出為何像蘋果這樣的巨頭采用臺積電、三星最先進,也是最貴的制程工藝,依舊能賺大錢,這就是為什么IC設(shè)計具有贏者通吃的特性。

像代工廠要進行的光刻、蝕刻、離子注入、金屬沉積、金屬層、互連、晶圓測試與切割、核心封裝、等級測試等步驟需要的成本,以及光刻機、刻蝕機、減薄機、劃片機、裝片機、引線鍵合機、倒裝機等制造設(shè)備折舊成本都被算進測試成本、封裝成本、掩膜成本中,就沒有必要另行計算了。

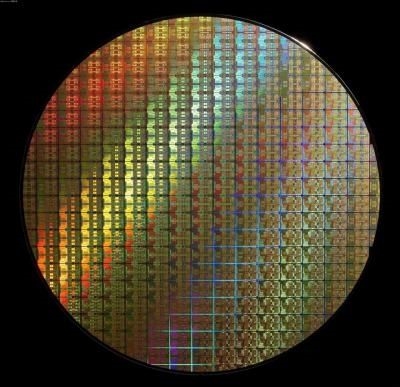

(晶圓)

晶片的成本

由于在將晶圓加工、切割成晶片的時候,并不是能保證100%利用率的,因而存在一個成品率的問題,所以晶片的成本用公式表示就是:

晶片的成本=晶圓的成本/(每片晶圓的晶片數(shù)*晶片成品率)

由于晶圓是圓形的,而晶片是矩形的,必然導(dǎo)致一些邊角料會被浪費掉,所以每個晶圓能夠切割出的晶片數(shù)就不能簡單的用晶圓的面積除以晶片的面積,而是要采用以下公式:

每個晶圓的晶片數(shù)=(晶圓的面積/晶片的面積)-(晶圓的周長/(2*晶片面積)的開方數(shù))

晶片的成品率和工藝復(fù)雜度、單位面積的缺陷數(shù)息息相關(guān),晶片的成品率用公司表達為:

晶片的成品率=(1+B*晶片成本/A)的(-A次方)

A是工藝復(fù)雜度,比如某采用40nm低功耗工藝的自主CPU-X的復(fù)雜度為2~3之間;

B是單位面積的缺陷數(shù),采用40nm制程的自主CPU-X的單位面積的缺陷數(shù)值為0.4~0.6之間。

假設(shè)自主CPU-X的長約為15.8mm,寬約為12.8mm,(長寬比為37:30,控制一個四核芯片的長寬比在這個比例可不容易)面積約為200平方毫米(為方便計算把零頭去掉了)。一個12寸的晶圓有7萬平方毫米左右,于是一個晶圓可以放299個自主CPU-X,晶片成品率的公式中,將a=3,b=0.5帶入進行計算,晶片成品率為49%,也就是說一個12寸晶圓可以搞出146個好芯片,而一片十二寸晶圓的價格為4000美元,分攤到每一片晶片上,成本為28美元。

芯片硬件成本計算

封裝和測試的成本這個沒有具體的公式,只是測試的價格大致和針腳數(shù)的二次方成正比,封裝的成本大致和針腳乘功耗的三次方成正比......如果CPU-X采用40nm低功耗工藝的自主芯片,其測試成本約為2美元,封裝成本約為6美元。

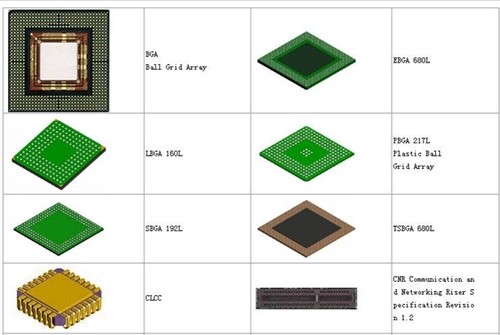

(芯片的封裝形式,以上兩圖都較為古老了)

因40nm低功耗工藝掩膜成本為200萬美元,如果該自主CPU-X的銷量達到10萬片,則掩膜成本為20美元,將測試成本=2美元,封裝成本=6美元,晶片成本=28美元代入公式,則芯片硬件成本=(20+2+6)/0.49+28=85美元。

自主CPU-X的硬件成本為85美元。

如果自主CPU-Y采用28nm SOI工藝,芯片面積估算為140平方毫米,則可以切割出495個CPU,由于28nm和40nm工藝一樣,都屬于非常成熟的技術(shù),切割成本的影響微乎其微,因此晶圓價格可以依舊以4000萬美元計算,晶片成品率同樣以49%的來計算,一個12寸晶圓可以切割出242片晶片,每一片晶片的成本為16美元。

如果自主CPU-X產(chǎn)量為10萬,則掩膜成本為40美元,按照封裝測試約占芯片總成本的20%、晶片成品率為49%來計算,芯片的硬件成本為122美元。

如果該自主芯片產(chǎn)量為100萬,則掩膜成本為4美元,按照封裝測試約占芯片總成本的20%來,最終良品率為49%計算,芯片的硬件成本為30美元。

如果該自主芯片產(chǎn)量為1000萬,則掩膜成本為0.4美元,照封裝測試約占芯片總成本的20%來,最終良品率為49%計算,芯片的硬件成本21美元。

顯而易見,在相同的產(chǎn)量下,使用更先進的制程工藝會使芯片硬件成本有所增加,但只要產(chǎn)量足夠大,原本高昂的成本就可以被巨大的數(shù)量平攤,芯片的成本就可以大幅降低。

芯片的定價

硬件成本比較好明確,但設(shè)計成本就比較復(fù)雜了。這當中既包括工程師的工資、EDA(LCEDA.cn)等開發(fā)工具的費用、設(shè)備費用、場地費用等等......另外,還有一大塊是IP費用——如果是自主CPU到還好(某自主微結(jié)構(gòu)可以做的不含第三方IP),如果是ARM陣營IC設(shè)計公司,需要大量外購IP,這些IP價格昂貴,因此不太好將國內(nèi)外各家IC設(shè)計公司在設(shè)計上的成本具體統(tǒng)一量化。

按國際通用的低盈利芯片設(shè)計公司的定價策略8:20定價法,也就是硬件成本為8的情況下,定價為20,自主CPU-X在產(chǎn)量為10萬片的情況下售價為212美元。別覺得這個定價高,其實已經(jīng)很低了,Intel一般定價策略為8:35,AMD歷史上曾達到過8:50。

在產(chǎn)量為10萬片的情況下,自主CPU-Y也采用8:20定價法,其售價為305美元;

在產(chǎn)量為100萬的情況下,自主CPU-Y也采用8:20定價法,其售價為75美元;

在產(chǎn)量為1000萬的情況下,自主CPU-Y也采用8:20定價法,其售價為52.5美元。

由此可見,要降低CPU的成本/售價,產(chǎn)量至關(guān)重要,而這也是Intel、蘋果能采用相對而昂貴的制程工藝,又能攫取超額利潤的關(guān)鍵。

| LM1117IMPX-3.3/NOPB/線性穩(wěn)壓器(LDO) | 0.7147 | |

| DRV8874PWPR/有刷直流電機驅(qū)動芯片 | 3.45 | |

| LM358BIDR/運算放大器 | 0.35 | |

| LMR33630ADDAR/DC-DC電源芯片 | 2.01 | |

| LM5164DDAR/DC-DC電源芯片 | 3.19 | |

| ADS1299IPAGR/模擬前端(AFE) | 222.43 | |

| TPS82130SILR/DC-DC電源模塊 | 6.13 | |

| TPL5010DDCR/定時器/計時器 | 1.0884 | |

| LM27762DSSR/電荷泵 | 3.11 | |

| TLV9062IDR/運算放大器 | 0.3242 |